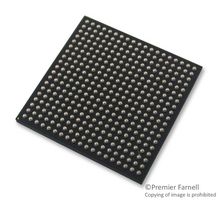

The OMAP-L1X series DSP+ARM? low-power Applications Processor based on an ARM926EJ-S and a C674x DSP core. This processor provides significantly lower power than other members of the TMS320C6000? platform of DSPs. The device enables original-equipment manufacturers (OEMs) and original-design manufacturers (ODMs) to quickly bring to market devices with robust operating systems, rich user interfaces and high processor performance through the maximum flexibility of a fully integrated, mixed processor solution. The dual-core architecture of the device provides benefits of both DSP and reduced instruction set computer (RISC) technologies, incorporating a high-performance TMS320C674x DSP core and an ARM926EJ-S core. The ARM926EJ-S is a 32-bit RISC processor core that performs 32- or 16-bit instructions and processes 32-, 16- or 8-bit data. The core uses pipelining so that all parts of the processor and memory system can operate continuously.

- 375- and 456MHz ARM926EJ-S? RISC MPU

- ARM926EJ-S core - 32- and 16-bit (Thumb?) instructions and DSP instruction extensions

- 16kB Instruction cache and data cache

- 8kB RAM (vector table)

- 64kB ROM

- C674x instruction set feature - Superset of the C67x+ and C64x+ ISAs

- C674x two-level cache memory architecture

- Enhanced direct memory access controller 3 (EDMA3)

- TMS320C674x floating-point VLIW DSP core

- Supports up to four SP additions per clock and four DP additions every two clocks

- Two multiply functional units

- Hardware support for modulo loop operation

- Protected mode operation

- Exceptions support for error detection and program redirection

- Software support - TI DSP BIOS?, chip support library and DSP library

- 128kB RAM shared memory

- Three configurable 16550-type UART modules

- LCD controller

- Two serial peripheral interfaces (SPIs) each with multiple chip selects

- One host-port interface (HPI) with 16-bit-wide Muxed address and data bus for high bandwidth

自动化与过程控制, 工业, 国防, 军用与航空